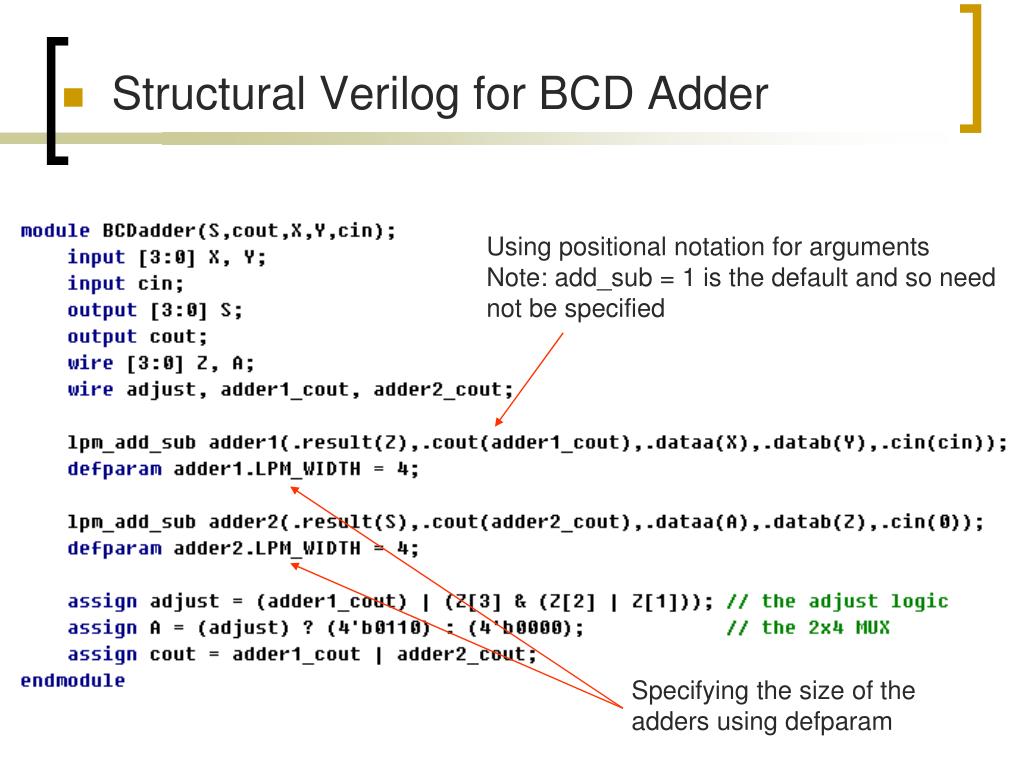

The results on FPGA shows that compressor based converters and multipliers produced less amount of propagation delay with a slight increase of hardware resources. The implementation was carried out using Virtex-6 Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuit (ASIC) with 90-nm technology library platforms. The designed hardware circuits were verified by behavioural and post layout simulations. To increase the performance, compressor circuits were used in converters and multiplier. The proposed converters, along with binary coded decimal (BCD) adder and binary to BCD converters, are used in parallel implementation of Urdhva Triyakbhyam (UT)-based 32-bit BCD multiplier. The objective of this work is to implement a scalable decimal to binary converter from 8 to 64 bits (i.e 2-digit to 16-digit) using parallel architecture.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed